本系列讲主要讲述Cache的工作原理和特性. 本章将对Cache的工作进行简介, 并对必要概念进行讲解

简介 (Introduction)

初衷

假设我们要从图书馆中找到几本书作为自己写论文的参考. 我们要花很长的时间去寻找书籍, 说不定还要不得不来回翻找. 越大的图书馆, 这个问题就越严重. 现代的电子设备也有着类似的问题. 在现实生活中, 我们愈发压缩存储的密度 (SRAM/DRAM/Solid State Disk/Magnetic Disk), 我们从内存中运行查找数据的速度就越慢. 但是我们想要一个又大又快的内存装置. 这就不得不让我们思考如何能够加快信息读取的过程.

Cache与内存

组成

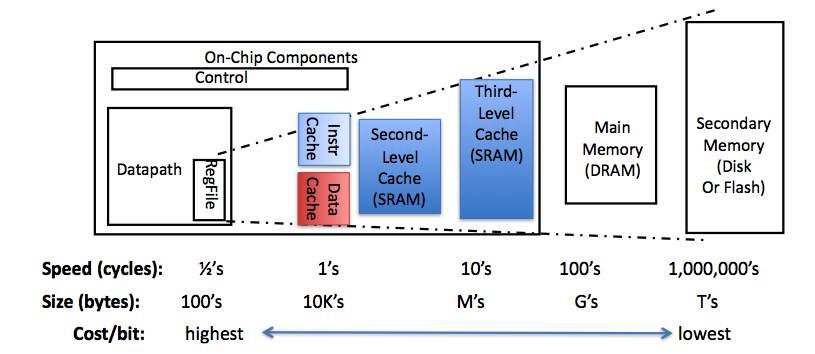

Cache和内存都是由RAM(Random Access Memory)组成的,可以根据地址随机访问,计算机掉电时RAM中保存的数据会丢失。不同的是,Cache通常由SRAM(Static RAM,静态RAM)组成,而内存通常由DRAM(Dynamic RAM,动态RAM)组成。DRAM电路比SRAM简单,存储容量可以做得更大,但DRAM的访问速度比SRAM慢。而内存一般由DRAM组成.

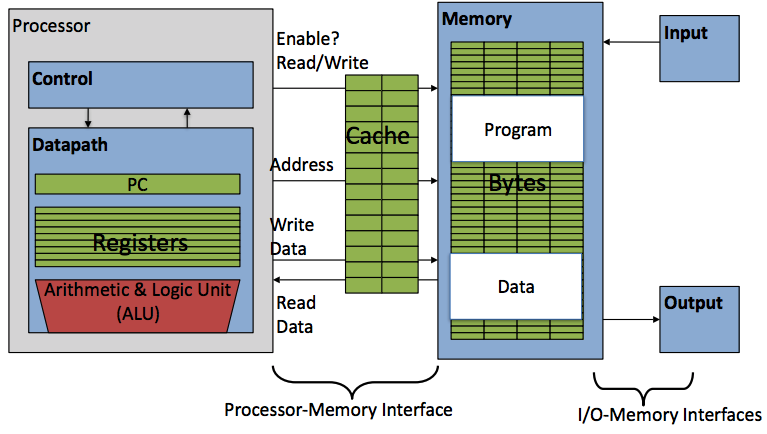

架构

Cache位于CPU核之中, 而内存是位于CPU外的芯片,与CPU通过地址和数据总线相连.

功能

Cache一般被称作“缓存”, 用于暂时储存最近访问过的数据. Cache的访问速度一般是内存的数倍, 所以合理的利用Cache也是提升整体计算机性能的关键.

问题所在

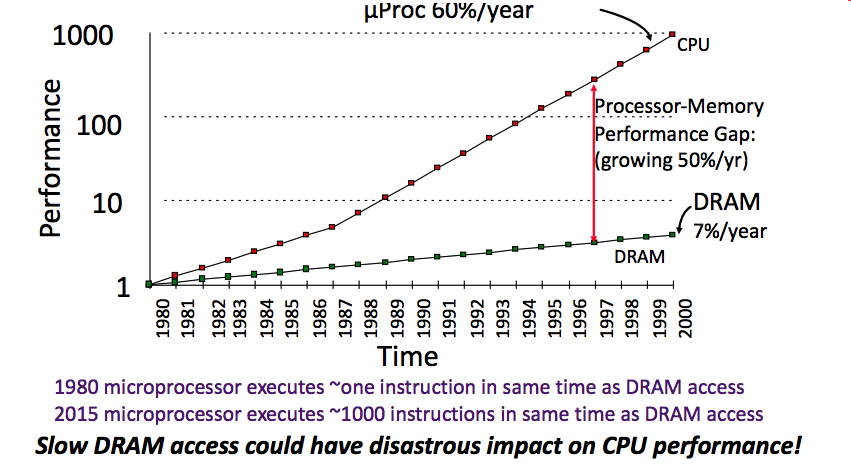

由于读写的速度有限制, Processor-DRAM (处理器与动态RAM)之间总是存在延迟 (Latency), 我们称之为Processor-DRAM Latency Gap.

核心概念

Memory Hierarchy (内存阶层)

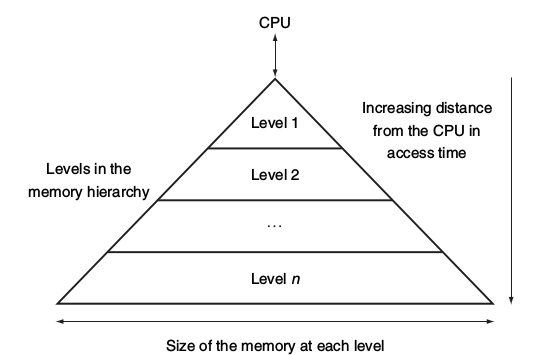

硬件的技术限制了,我们有容量很小但很快的存储器,亦或是容量很大但很慢的存储器,但鱼和熊掌不可兼得.因此,现代计算机将存储器分成若干级,称为Memory Hierarchy (内存阶层),按照离CPU由近到远的顺序依次是CPU寄存器、Cache、内存、硬盘,越靠近CPU的存储器容量越小但访问速度越快.

Locality (局部性)

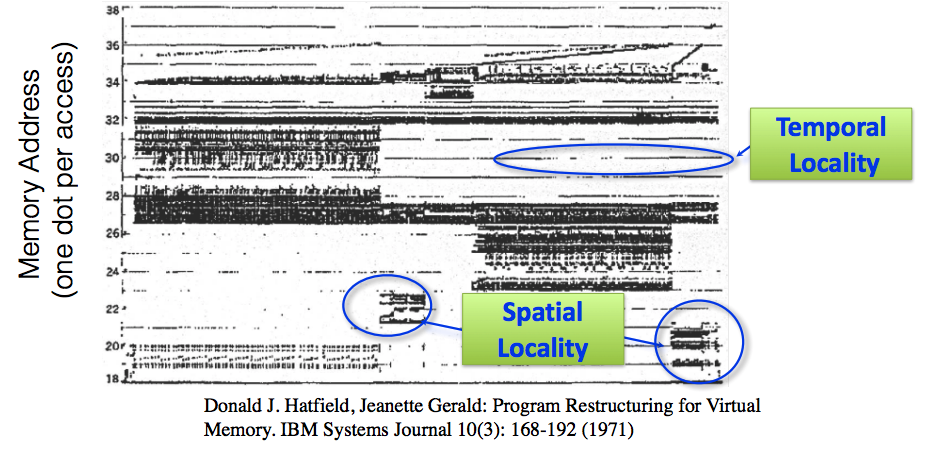

- Temporal Locality (locality in time) 时间局部性

- 如果一个信息项正在被访问,那么在近期它很可能还会被再次访问. (通常在循环中)

- Spatial Locality (locality in space) 空间局部性

- 如果一个信息项正在被访问,那么其空间位置附近的信息项也可能近期被访问.

- 如果一个信息项正在被访问,那么其空间位置附近的信息项也可能近期被访问.

局部性原则: 程序在短瞬时间内将访问一小部分存储器空间位置(Temporal Locality), 并将重复访问该部分地址(Spatial Locality)

Hit & Miss (Rate & Time)

我们刚刚提到了计算机存储机制将存储器分为了距离CPU距离又近到远, 容量由小到大, 访问速度由快到满的很多Level(层级).  我们搜寻资料的时候, 将会由上至下检查该层储存器中是否有自己想要的资料. 如果有, 我们称之为Hit, 若没有, 我们称之为Miss, 并将进入下一级存储器查找.

我们搜寻资料的时候, 将会由上至下检查该层储存器中是否有自己想要的资料. 如果有, 我们称之为Hit, 若没有, 我们称之为Miss, 并将进入下一级存储器查找.

随之而来的名词还有Hit Rate, 也就是在当层存储器中找到所求资料次数的比例; 反之也就是Miss Rate. 由此我们也可得出Hit Rate + Miss Rate = 1. 根据定义我们可知, 提高Hit Rate对于计算机的处理效率很有帮助.

还有对于计算机运行时间效率很有影响的就是Hit Time和Miss Penalty. Hit Time指的是判断当前存储器是否为Hit和将所需资料调动到处理器一共所花的时间. 而Miss Penalty指的是将资料从下层存储器带来并调动到处理器一共所花的时间.

本系列Part 2将开始介绍Cache的结构机制