本章我们将从计算机科学大框架入手, 并开始以python为基础介绍编程的思想和实现. 注意, 本节课不是编程语言课, 所以不会花太多的功夫介绍python的语言特性, python标识方面的问题, 可以结合网络进行理解学习.

CS 61A 学习手册 [Part 0] 简介

CS 61A 是加州大学伯克利分校 (University of California, Berkeley) 计算机系的第一节入门课程. 曾被评为世界最好的5节计算机课之一. CS 61A是一节既包罗万象, 又深刻探索计算机思维和技能的课程.

RISC-V Based CPU Design with Logisim [Part 7]

PipeLining

7. Pipelining

7.1 Introduction

A pipeline is a set of data processing elements connected in series, where the output of one element is the input of the next one.

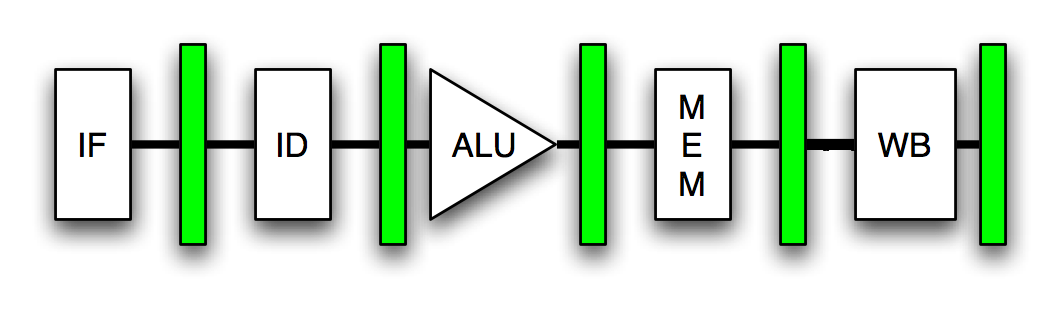

Let's first review our processing structure of our CPU. We can see that we have a structure like this:

RISC-V Based CPU Design with Logisim [Part 6]

Memory Management and Write Back systems

6. RAM and Write-Back

A Random-access memory (RAM) is a form of computer data storage that stores data and machine code currently being used.

Remember Bob's story in Part 4? The RAM is just like the cabinet where Bob store the data in his first & second bag and then re-load the data.

RISC-V Based CPU Design with Logisim [Part 5]

ALU Design and Input Selection

5. ALU System

An Arithmetic Logic Unit (ALU) is a combinational digital electronic circuit that performs arithmetic and bitwise operations on integer binary numbers.

We will talk about the designing of the ALU system and the input control of ALU in the CPU system. Note that in this part we might use some result achieved from Part 3 (ALUSel). Reviewing Part 3 is recommended.

RISC-V Based CPU Design with Logisim [Part 4]

Data Management in Registers - RegFile in CPU

4. Registers System Implementation

A processor register is a quickly accessible location available to a computer's Central Processing Unit (CPU)

Let's take an example to understand the usage of registers. Say if Bob wants to go out for work, and he has too many things to carry which he cannot take them all with him. However, Bob has some hand bags (registers)which he can carry some files with him. Each time before Bob goes out, he receives a message telling him the job today. So Bob goes out with his handbags for work. Say today, Bob's work is to add the number of files in his first handbag to that in the second bag and put the total number as a new file and store it into the second bag. Say if Bob's first bag carries a number 4 and his second handbag carries a number 2, after the operation, the number in his first bag would still be 4 but the number in his second hand bag would be 4+2=6. After all, Bob goes back home.

RISC-V Based CPU Design with Logisim [Part 3]

Decoding and ALU Selection

3. Instruction Analysis

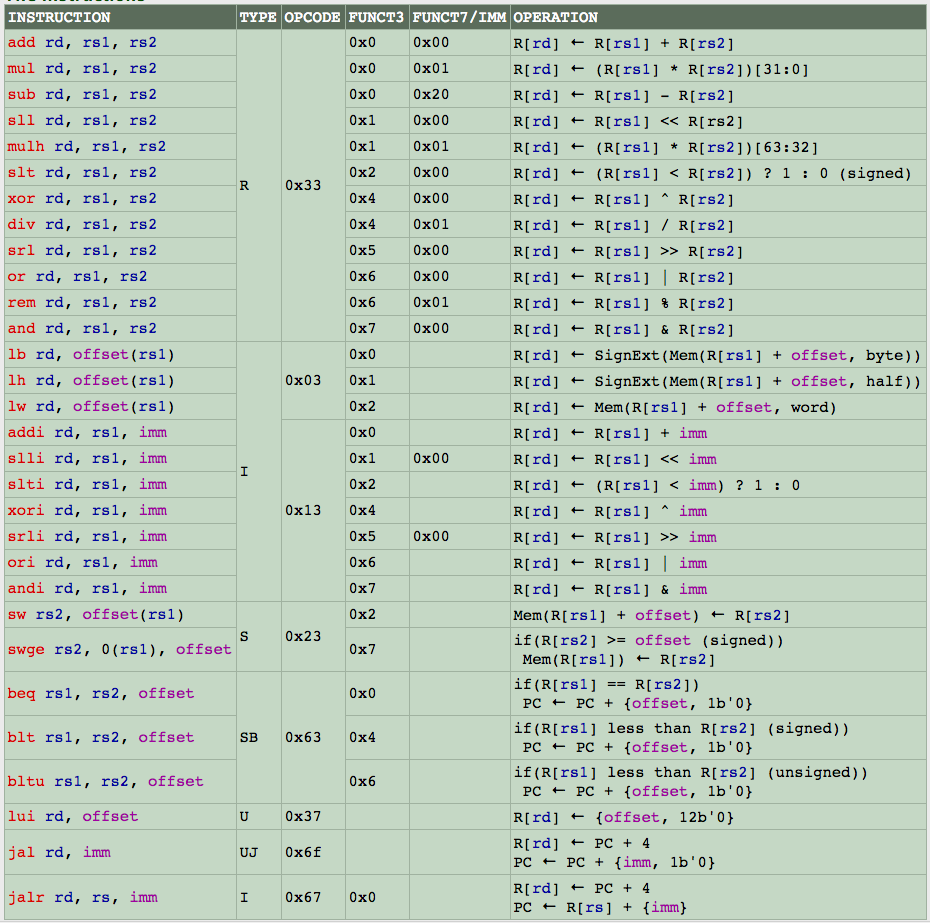

We assume that you have basic understanding about RISC-V, if you are not so familiar with RISC-V, please click HERE(not published) to see my related article.

Each type of RISC-V instructions has an special encoding format to convert the assembly scripts into machine codes. Here, given the machine codes, we need to determine which instruction it is by comparing with the formatting regulations.

RISC-V Based CPU Design with Logisim [Part 2]

Datapath and Instruction Fetching

1.2 Datapath

The functionality of a CPU is basically a progress calling, computing, and storing data based on given instructions. You can think of your cabinets and you are basically trying to deal with your clothes. If you want to wash your white shirt (this instruction is from a note you picked from another cabinet), what should you do? You should probably first find the white shirt in your cabinet, then pick it out, put it into the washing machine. Then, after some minutes, pick them out and put the clean shirt somewhere in the cabinet again. Then, say if you want to store some washing powders for further usage, you may put that into the cabinet (find a proper spot) where you got the notes for the instructions.

The cloth here is just like the data, the cabinet where you pick the instructions and store the washing powder is the memory, and the cabinets where you get the cloths from are the registers, and the washing machine is like your ALU (performing arithmetic operations as required, continuing the example, this "operation" can also be drying or rinsing).

We will first development a single-cycle system in Stage-1. In Stage-2, we will implement Pipelining to increasing the performance of our CPU.

RISC-V Based CPU Design with Logisim [Part 1]

Introduction with Definitions and Datapath

1. Introduction

This project is based on UC Berkeley, CS61C, Spring 2018, Project 3. The project is revealed by Logisim.

In this project we will be using Logisim to implement a 32-bit two-cycle processor based on RISC-V (Stage1: Single-Cycle; Stage2: Pipelining) The project is mainly consisted by four parts: CPU, PC, RegFile, ALU, RAM. We will first introduce the general definitions and ideas of the project. Then we'll discuss the designing of each part of CPU. Finally talk about the CPU system setup and PipeLining.